# Subthreshold Design of Second Generation Current Conveyor

MohdAjmalKafeel,Mohammad ZulqarnainDepartment of Electronics Engineering AMU, Aligarh, India

Abstract—Current mode circuits like current conveyors have attained significant importance especially in the field of current analog ICs design as compared to their voltage mode counterparts due to higher speed, lower power consumption and lesser chip area. This paper presents the design and optimization of ultra-low power second generation current conveyor (CCII) in the subthreshold region. Optimal sizing of transistors for different designs has been done at low supply voltages ranging from  $\pm 0.7V$  to  $\pm 0.25V$ . A design operating at supply voltage of  $\pm 0.25V$  and bias current of 20pA was found to be optimal. HSPICE simulations were performed to measure various performance parameters of CCII at the 32nm technology node.

Index terms –ultra-low power, subthreshold, current conveyor, current mirror, non-minimal length design.

## I. INTRODUCTION

Ultra-low-power (ULP) design is important for biomedical systems. These systems should be small, consume minimum power and dissipate minimum heat. A fully implanted system with a battery that has a limited number of wireless recharges must operate under stringent low-power constraints such that constant surgery is not needed to change the battery in a patient. Thus, ULP operation will always be paramount in implantable biomedical systems [1]. ULP demands that the transistors should operate in the subthreshold regime where the supply voltage is lower than the threshold voltage of a MOS transistor.

# A. Subthreshold operation of a MOS transistor

In subthreshold regime, the drain current in a MOSFET is given by

$$I_D = I_0 \frac{W}{L} e^{\frac{Vgs - Vth}{nVt}} (1 - e^{-Vds/Vt})$$

(1)

where  $I_0$  is the technology dependent subthreshold current extrapolated for Vgs = Vth, Vt = kT/q is the thermal voltage,  $\frac{W}{L}$  is the aspect ratio and 'n' is the subthreshold factor [2]. The operation of MOS device in subthreshold region is necessary for ultra low power circuits [3]. A whole class of CMOS circuits has been developed for the weak inversion operation of MOS device [4]. The MOS device can be used to achieve higher gain in subthreshold region as  $I_D$  is exponentially dependent upon Vgs. But the speed of subthreshold circuits is severely limited because of large device sizes and low drain current [5]. It is possible to operate Mohd.Hasan, Muhmmad Shah AlamProfessor/Department of Electronics Engineering AMU, Aligarh

devices at quite low voltages in the range of 0.25-0.3V without sacrificing their functionality in subthreshold regime that reduces power consumption at the cost of reduced speed.

There is a need of a basic building block that can be used to implement large number of different analog functions and that too in the subthreshold region. Second generation current conveyor (CCII) can be regarded as a real competitor for the operational amplifier (OPAMP). The classical OPAMP has suffered from constant gain band-width product problem and has low slew rate at its output. It has unreliable frequency response and remains unsatisfactory for high frequency applications. CCII, being a current mode device, has larger dynamic range, higher band-width, greater linearity, simpler circuitry, lower power consumption, and reduced chip area as compared to their voltage mode counterparts like Operational amplifiers. Due to its flexibility and versatility, CCII finds applications in realising impedance convertors, integrators, differentiators, filters etc. [6-9]. Few low voltage CCII structures have been reported so far operating at a supply voltage of 1V or less but they are unable to meet ultra-low power constraint on account of their complex structure [10-12]. Current conveyor structures, characteristics and performance have been investigated in super-threshold region [13-14]but to the best of our knowledge its design, performance and characteristics have not yet been explored under subthresholdcondition. Hence, this paper investigates, for the first time, the design and optimization of a CCII under subthreshold condition.

The rest of the paper is organized as follows. A brief introduction of CCII is given in section 2. Section 3 and 4 dealwith the design and performance analysis of various parameters of CCII for different designs.In section 5, variability analysis of optimal design is done using Monte Carlo analysis followed by the design of an instrumentation amplifier based on the designed CCII in section 6. Section 7 then concludes the paper.

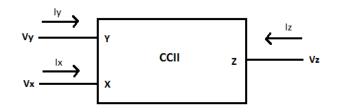

Figure 1 CCII block diagram

# II. BASICS OF SECOND GENERATION CURRENT CONVEYOR

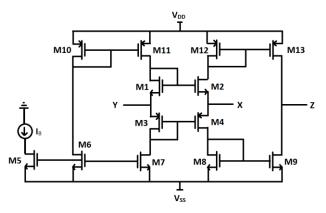

The first generation current conveyor was introduced by Sedra and Smith in 1968. Later in 1970, they came up with a novel type of current conveyor known as second generation current conveyor [20-21]. Second generation current conveyor (CCII) is basically a versatile current mode (CM) device which conveys current with unity gain from the input port to the output port. With one high input impedance, one low input impedance and one high output impedance, it is a suitable element for both voltage-mode and current-mode circuits and can be used to perform many useful functions. The block diagram representation of CCII and its internal transistor implementation are shown in Figures 1 and 2 respectively.

The characteristic equations of the dual output current conveyor can be represented as follows:

| $I_{Y}=0$       |   |            | (2) |  |

|-----------------|---|------------|-----|--|

| $V_X = V_Y(3)$  |   |            |     |  |

| $I_Z = \pm I_X$ |   |            | (4) |  |

| 1               | l | <b>X</b> 7 |     |  |

where  $V_X$  and  $V_Y$  are the voltages at ports X and Y, respectively.  $I_X$  and  $I_Y$  are the currents entering ports X and Y. Moreover,  $I_{Z_+}$  is the positive-type output current and  $I_{Z_-}$  is the negative type output current. Ideally, a current conveyor should satisfy the following conditions:

1) Infinite input impedance  $(R_Y)$  at port Y.

- 2) Zero input impedance  $(R_X)$  at port X for current inputs.

- 3) Infinite output impedance  $(R_Z)$  at port Z.

- 4) Unity current transfer gain between ports X and Z.

- 5) Unity voltage transfer gain between ports Y and X.

6) Infinite bandwidth.

## III.CCII STRUCTURES AND DESIGN CONSIDERATIONS

Figure 2 uses a mixed translinear loop (transistors M1–M4) as the input of the CCII. Transistors M9, M10 and M11, M13 form two current mirrors that allow the mixed loop to be dc biased by the current. The input transistors present a high input impedance at port Y and a low impedance at port X. This configuration acts as a voltage follower. The output Z copies the current flowing through port X and is realized in the conventional manner using two complementary mirrors as current follower.

The following section presents the design of a translinear loop based CCII in the subthreshold regime. The critical issue in designing translinear based CCII structure in the superthreshold region is the matching of NMOS and PMOS loop components in which  $\mu_n$  and  $\mu_p$  are process dependent parameters [14]. The situation becomes more critical in subthreshold region especially for submicron devices. Considering the various trade off conditions, different designs of translinear CCII structures are simulated using PTM 32nm level-54 model [16]. The performance evaluation of each design is carried out on the basis of various key characteristics of CCII namely current gain ( $\alpha$ ), voltage gain ( $\beta$ ), current bandwidth, voltage bandwidth, resistances and their respective bandwidths at various ports of CCII.

### A. Design of classic translinear structure

The design begins by transistor sizing on the basis of mobilities of NMOS and PMOS transistors. The adjusted aspect ratios of different transistors in [13, 23] are such that will keep all the transistors in the saturation region and they utilize 0.35  $\mu$ m and 0.25  $\mu$ m CMOS process parameters respectively. The optimal sizing of each transistor in this design of the current conveyor is done according [13, 23] using 32nm technology node. The supply voltage and bias current are adjusted such that all the transistors operate in the subthreshold region (V<sub>gs</sub><V<sub>th</sub>). The aspect ratios of the transistors are listed in Table 1.

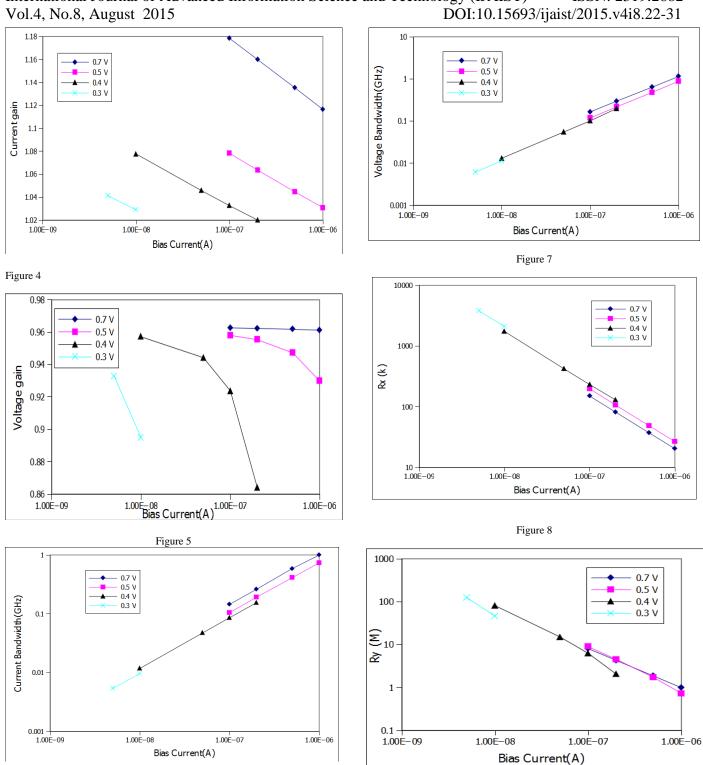

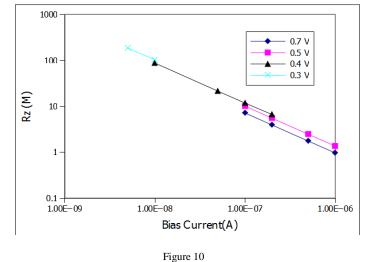

The supply voltage is varied from  $\pm 0.7V$  to  $\pm 0.3V$  and the bias current is also changed for a particular supply voltage keeping all the transistors in the subthreshold region. All simulations are performed using HSPICE and performance parameters variations are plotted in Figures 4-10. Table 2 lists the performance parameters at  $\pm 0.3V$  supply voltage and at a bias current of 5nA and is compared with [13].

Figure 2 CMOS based circuit of CCII

Table 1. Transistors channel widths and lengths

| Transistor | W/L               |

|------------|-------------------|

| M1-M2      | 1.28µm / 0.064µm  |

| M3-M4      | 2.048µm / 0.064µm |

| M5-M9      | 0.768µm / 0.064µm |

| M10-M13    | 1.28µm / 0.064µm  |

Table 2. Performance parameters of CCII

|                 | [13]   | This Design |

|-----------------|--------|-------------|

| V <sub>DD</sub> | ±1.5 V | ±0.3 V      |

| I <sub>B</sub>  | 50 µA  | 5 nA        |

| α               | 1.02   | 1.0413      |

| β               | 0.9515 | 0.9328      |

| α-3dB (MHz)     | 393    | 5.38        |

| International Journal of Advanced Information Science and | Technology (IJAIST) | ISSN: 2319:2682    |

|-----------------------------------------------------------|---------------------|--------------------|

| Vol.4, No.8, August 2015                                  | DOI:10.15693/ijais  | st/2015.v4i8.22-31 |

| β-3dB (MHz)              | 503      | 6.14      |

|--------------------------|----------|-----------|

| R <sub>x</sub>           | 1.44 kΩ  | 3.81 MΩ   |

| R <sub>Y</sub>           | 37.54 kΩ | 124.06 MΩ |

| R <sub>Z</sub>           | 197.1 kΩ | 185 MΩ    |

| 3dB R <sub>X</sub> (MHz) | -        | 18.7      |

| 3dB R <sub>Y</sub> (MHz) | -        | 0.182     |

| 3dB R <sub>Z</sub> (MHz) | -        | 0.374     |

It can be observed from Table 2 that as the supply voltage and bias currents are reduced, there is a significant reduction in power dissipation as the transistors are moved into the subthreshold region at the cost of reduced bandwidth and higher port resistances. However, there is a considerable current mismatch in the current mirror as we move deep into the subthreshold region by reducing the bias current and supply voltage due to drain induced barrier (DIBL) lowering as explained below.

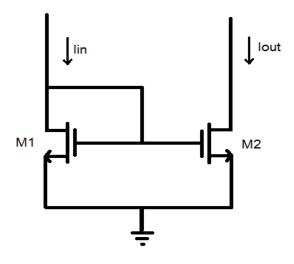

#### B. Subthreshold current mirror

By using equation 1, the ratio of drain currents of M1 and M2 can be written as follows:

$$\frac{I_{out}}{I_{in}} = \frac{I_0(\frac{W}{L})_2 e^{\frac{Vgs\,2-Vt\,h\,2}{nVt}}(1-e^{-Vds\,2/Vt})}{I_0(\frac{W}{L})_1 e^{\frac{Vgs\,1-Vt\,h\,1}{nVt}}(1-e^{-Vds\,1/Vt})}$$

(5)

If both transistors have the same aspect ratio and Vds>4Vt  $\approx 100$  mV, then  $\left(1 - e^{-\frac{Vds}{Vt}}\right) \approx 1$ , and hence, the above equation can be re-written as:

$$\frac{I_{out}}{I_{in}} = \frac{e^{\frac{1}{nVt}}}{e^{\frac{Vgs}{nVt}}}$$

(6)

In equation 1, the threshold voltage Vth also depends on the drain-source voltage Vds (through the drain induced barrier lowering (DIBL) effect) and the bulk-source voltage Vbs (through the body effect) according to

$Vth = Vth0 - \lambda dsVds - \lambda bsVbs \tag{7}$

where  $\lambda ds > 0$  is the DIBL coefficient and  $\lambda bs > 0$  is the body effect coefficient [24].

Since Vgs1 = Vgs2 and source and body are at same potential, so Vbs = 0, hence the above equation reduces to,

$$\frac{I_{out}}{I_{in}} = e^{\frac{Vt h 1 - Vt h 2}{nVt}}$$

$$\frac{I_{out}}{I_{in}} = e^{\frac{\lambda ds (Vds 2 - Vds 1)}{nVt}}$$

$$\frac{I_{out}}{I_{in}} = e^{\frac{\lambda ds \Delta Vds}{nVt}} (8)$$

$I_{in}$ Where,  $\Delta V ds = V ds 2 - V ds 1$

Hence, current mismatch in subthreshold current mirror is exponentially dependent on drain to source voltage mismatch. The expressions for the current gain ( $\alpha$ ) and voltage gain ( $\beta$ ) is given as [25]

$$\alpha = \frac{l_Z}{l_X} = \frac{g_{m2}g_{m8}g_{m13} + g_{m4}g_{m9}g_{m12}}{g_{m8}g_{m12}(g_{m2} + g_{m4})}(9)$$

$$\beta = \frac{V_X}{V_Y} = \frac{g_{m2} + g_{m4}}{g_{m2} + g_{m4} + (rds 2)^{-1} + (rds 4)^{-1}}(10)$$

It can be deduced from Figure 4 that for a particular supply voltage as the bias current increases, current gain tends towards unity. When the bias current increases, drain to source voltage mismatch of current mirrors reduces and hence from equation (8), current mismatch also reduces. Thus, current gain comes closer to unity.

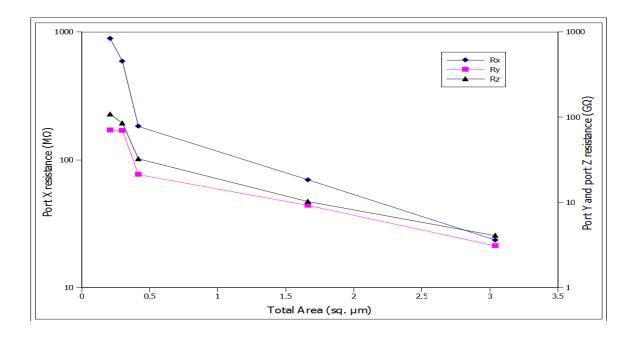

Figure 3. Basic Current Mirror circuit

Figure 5 shows the variation of the voltage gain with the bias current and the trends are just the reverse of Figure 4. For a constant supply voltage, if bias current increases then the deviation of the voltage gain from unity increases. As bias current increases, drain to source resistances r<sub>ds</sub> reduces and hence from equation (10) voltage gain  $\beta$  deviates away from unity with  $\beta < 1$ . It is possible to find the optimum supply voltage and bias current by the intersection of current and voltage gains curves which gives least possible deviations in current gain and voltage gain. Figures 6-7 show the variation of the voltage and the current bandwidths with the bias current respectively. Simulation results indicate that both the 3-dB current and voltage bandwidths decrease as the bias current and supply voltage reduce. The observed reduction in the bandwidths is due to the lower value of transconductance at lower current /voltagelevels. Furthermore, it is observed from Figures 8-10 that the resistances at ports X, Y, and Z increase in a similar manner on the reduction of bias current and supply voltage due to lower current level. The observed trends indicate that an optimum supply voltage and bias current have to be investigated to achieve optimum performance of a CCII.

International Journal of Advanced Information Science and Technology (IJAIST) ISSN: 2319:2682

Figure 6

Figure 9

International Journal of Advanced Information Science and Technology (IJAIST) ISSN: 2319:2682 Vol.4, No.8, August 2015 DOI:10.15693/ijaist/2015.v4i8.22-31

| Design 1 | 7.5   | 26.25  | 5    | 17.5  |

|----------|-------|--------|------|-------|

| Design 2 | 3     | 10.5   | 2    | 7     |

| Design 3 | 0.75  | 2.625  | 0.5  | 1.75  |

| Design 4 | 0.375 | 1.3125 | 0.25 | 0.875 |

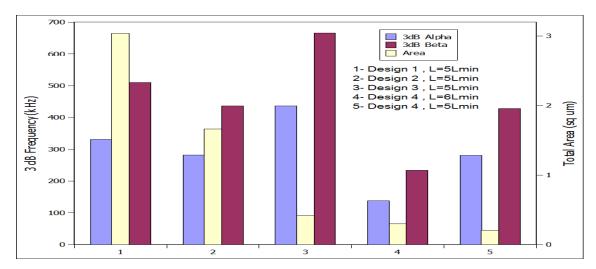

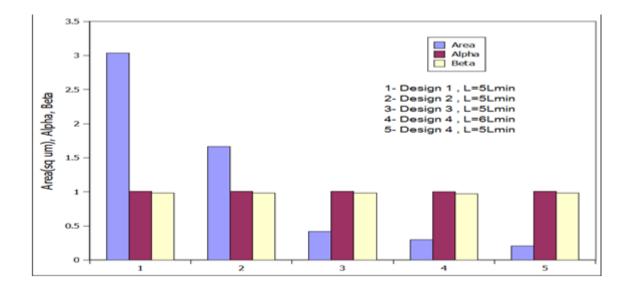

For a particular design (4,5 in Figure 11), if we increase area by increasing the lengths of the transistors, then current and voltage gains come closer to unity. From Figure 12, it is obvious that if area increases for a given design (4, 5 in Figure 12) then voltage and current bandwidths decrease because of the increase in device capacitances. Figure 13 shows that if area reduces then resistances seen by different ports increase. Thus, we can see that for Design 4 having  $L=5L_{min}$ , the area is minimum. But in this design two transistor's widths come out to be less than  $1.5L_{min}$ . In order to ensure that the width of each and every transistor is at least 1.5Lmin, Design 4 having L=6L<sub>min</sub> is taken into consideration. It can be operated at 20pA bias current and at even lower supply voltage of  $\pm 0.25$  V. The power dissipation for this particular design is also minimum and it shows better trade off in performance parameters amongst all the implemented designs, thereby, making it the most optimal design.

# IV. NON-MINIMAL LENGTH DESIGNS OF CCII

This section investigates different designs by incorporating non-minimal length of transistors and various performance parameters have been evaluated keeping all the transistors in the subthreshold regime. The various designs and their aspect ratios are listed in Table 3. To begin with, aspect ratios of M5-M9 (NMOS) are chosen depending upon silicon area consumption allowance. Depending on the  $\mu_n/\mu_p$  ratio of 32nm technology, aspect ratios of M10-M13 (PMOS) are chosen to be 3.5 times that of M5-M9. For M1-M2 and M3-M4, aspect ratios are chosen to be 1.5 times of M5-M9 and M10-M13 respectively. Design 1 to Design 4 follows the same procedural steps of choosing the aspect ratios of various transistors. As shown in Table 3, aspect ratios of M5-M9 are subsequently scaled down from 5 to 0.25 from Design 1 to Design 4.

Supply voltage is varied from  $\pm 0.3V$  to  $\pm 0.25V$  and bias current is varied from 750 pA to 20 pA for different designs. As one moves from Design 1 to Design 4, significant reduction in power consumption is obtained, resistances at Y and Z terminal change from tens of giga ohms to hundreds of giga ohms while resistance at X terminal is also increasing from tens of mega ohms to around thousands of mega ohms. This increase in resistance  $R_x$  is due to the inverse dependence of resistance on the bias current [19]. Current and voltage bandwidths lie in the range of hundreds of kilohertz which is suitable for biomedical applications. The lengths of transistors have to be non-minimal in subthreshold design to reduce current mismatch. For this reason, lengths of the transistors have been taken five to six times of L<sub>min</sub>, which ensures that the currents mismatch is within ±10% limit on account of high output resistance. The variation of different performance parameters of CCII with total area of the device for each design is shown in Figures 11-13. It can be deduced from Figure 11 that as the total area increases, voltage and current gains follow same trends of approaching unity.

Table 3W/L ratios of different designs

| M | I-M2 M3-M4 | 4 M5-M9 | M10-<br>M13 |

|---|------------|---------|-------------|

|---|------------|---------|-------------|

| Table 4 | Performance parameters for different Designs. |  |

|---------|-----------------------------------------------|--|

|---------|-----------------------------------------------|--|

|    |                         | Design 1<br>L=5L <sub>min</sub> | Design 2<br>L=5L <sub>min</sub> | Design 3<br>L=5L <sub>min</sub> | Design 4<br>L=5L <sub>min</sub> | Design 4<br>L=6L <sub>min</sub> |

|----|-------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 1  | $V_{DD}(V)$             | ±0.3                            | ±0.3                            | ±0.3                            | ±0.3                            | ±0.25                           |

| 2  | I <sub>B</sub> (pA)     | 750                             | 250                             | 100                             | 30                              | 20                              |

| 3  | α                       | 1.0107                          | 1.0106                          | 1.0100                          | 1.0100                          | 1.002                           |

| 4  | β                       | 0.9830                          | 0.9845                          | 0.9812                          | 0.9824                          | 0.9722                          |

| 5  | α-3dB (KHz)             | 331                             | 282                             | 437                             | 281                             | 138                             |

| 6  | β-3dB (KHz)             | 510                             | 437                             | 666                             | 428                             | 234                             |

| 7  | $R_X(M)$                | 23.63                           | 69.76                           | 182.49                          | 588.22                          | 887.52                          |

| 8  | $R_{Y}(G)$              | 3.096                           | 9.263                           | 21.2232                         | 69.54                           | 72.48                           |

| 9  | $R_Z(G)$                | 4.080                           | 7.09                            | 32.5                            | 85.1                            | 113                             |

| 10 | Current deviation       | ±7.5%                           | ±9.8 %                          | ±5%                             | ±9.66%                          | ±8.9 %                          |

| 11 | Area (µm <sup>2</sup> ) | 3.040                           | 1.664                           | 0.416                           | 0.208                           | 0.299                           |

Figure 12

Figure 13

# V. VARIABILITY ANALYSIS OF OPTIMAL DESIGN

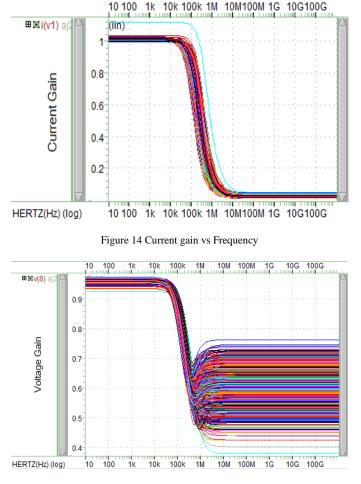

In order to test the robustness of Design 4 having L=6L<sub>min</sub>, variability analysis is carried out as this has become a metric of equal importance as the challenge is to design reliable circuits with unreliable devices at highly scaled technology node such as 32 nm [15]. Performance parameters (Current gain and voltage gain) of CCII are estimated with MC (Monte Carlo) simulation using 32 nm PTM. The channel length (L) and channel width (W) are assumed to have independent Gaussian distributions with  $3\sigma$  variation of 10% [17]. Performance metrics in this work are estimated with 2000 sample size [18].

Figures 14-15 show Monte Carlo simulation results of the current and voltage gain. It can be observed from these figures that variations in the current and voltage gains are within acceptable limits (closer to unity with  $\pm 10\%$  in variation) in the low frequency range where most of the biomedical systems operate.

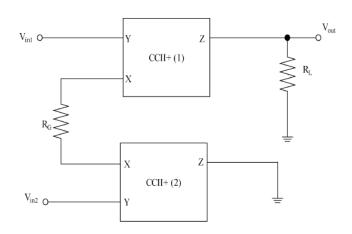

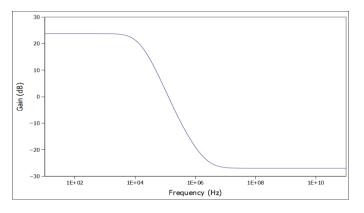

# VI. DESIGN OF INSTRUMENTATION AMPLIFIER BASED ON CCII

To validate the optimal design of CCII (Design 4 having  $L=6L_{min}$ ), an instrumentation amplifier, shown in Figure 16, is simulated using HSPICE [22]. The amplifier is designed for a differential gain of 27 dB. The frequency response is shown in Figure 17. The simulated gain obtained is 24 dB which shows good agreement with the designed value.

#### **VII. CONCLUSION**

This paper has successfully presented the various designs of second generation current conveyors (CCII) under subthreshold condition. Various performance parameters have been calculated for various designs by choosing the W/L ratios in such a way so as to preserve the functionality of the CCII device. The design 4 with L=6L<sub>min</sub>, operating at  $\pm 0.25$ V and at a bias current of 20pA, was found tobe optimal and more robust as compared to other designs, thus making it most suitable for ultra low power applications.

Figure 15 Voltage gain vs Frequency

Figure 16 Instrumentation Amplifier based on CCII

Figure 17 Frequency response of Instrumentation Amplifier

## REFERENCES

- Sarpeshkar, R. (2011). Ultra Low Power Bioelectronics, Fundamentals, Biomedical Applications and Bio-inspired Systems, 2nd ed.: Cambridge University press.

- [2]. Tsividis, Y. (1999). Operation and Modeling of the MOS Transistor. 2nd ed., New York: McGraw-Hill.

- [3]. Allen, P, andHolberg, D. (2010). CMOS Analog Circuit Design. 2nd ed.: Oxford University Press.

- [4]. Vittoz, E., andFellrath, J. (1977). "CMOS Analog Integrated Circuits Based on Weak Inversion Operation". IEEE Journal of Solid State Circuits, 12(3), pp.231-244.

- [5]. Razavi, B. (2002). Design of Analog CMOS Integrated Circuits.Tata McGraw-Hill.

- [6]. Sedra, A.S. (1989). "The current conveyor: history and progress". In Proc. IEEE Int. Symp. Circuits Syst., 3, pp.1567–1571.

- [7]. Minaei, S., Sayein, O. K., andKuntman, H. "A new CMOS electronically tunable current conveyor and its application to current mode filter". (2006). IEEE Tran. Circuits Syst. I, 53(7), pp.1448–1457.

- [8]. Wilson, B. (1990). "Recent developments in current conveyor and current mode circuits". In Proc. IEEE, 137(2), pp.63–77.

- [9]. Thoumazou, C., Lidge, F., andHaigh, D.(1990). "Analog Integrated Circuit Design: The Current Mode Approach". London, U.K: IEE.

- [10]. Elwan, H. O., &Soliman, A. M. (1997). "Low-voltage lowpower CMOS current Conveyors". IEEE Trans. Circuits and Systems-I.44(9), pp.828-835.

- [11]. Metin, B., Pal, K., andCicekoglu, O. (2012)." A new approach for high-input impedance in voltage mode filters using first-generation current conveyor in place of second generation current conveyor". Int. Journal of Elec., 99, pp.131–139.

- [12]. Rajput, S. S. and Jamuar, S. (2001). "Low voltage, low power, high performance current Conveyors". In Proc. IEEE, Sydney, Australia, 1, pp.723–726.

- [13]. Chaisricharoen, R., Chipipop, B., and Sirinaovakul, B. (2010). "CMOS CCCII: Structures, characteristics and considerations". Int. Journal of Electron. Commun. (AEÜ), 64, pp.540–557.

- [14]. Meechuea, N., Chipipop, B., Chaisricharoen, R., andSirinaovakul, B. (2013). "High Frequency Precision Modelling of CMOS-Based Translinear CCCII-".In Proc. of 13th International Symposium on Communications and Information Technologies (ISCIT).

- [15]. Islam, A, Kafeel, M.A., Iqbal, V. and Hasan, M. (2012). "Variability Analysis of MTJ-Based circuits". In Proc. of third international conference on Computer and Communication Technology (ICCCT) ,pp.57-62.

- [16]. Nanoscale Integration and Modeling (NIMO) Group, Arizona State University (ASU). [Online]. Available: http://ptm.asu.edu/.

- [17]. Vaddi, R., Dasgupta, S. andAgarwal, R.P. (2010). "Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS". IEEE Tran. Electron Devices, 57(3), pp.654-664.

- [18]. Alioto, M., Palumbo, G. andPennisi, M. (2010). "Understanding the effect of process variations on the delay static and domino logic". IEEE Tran. Very Large Scale Integr. (VLSI) Syst., 18(5), pp.697–710.

- [19]. Hassen, N., Ettaghzouti, T. andBesbes, K. (2011)."Highperformance Second-Generation Controlled Current Conveyor CCCII and High Frequency Applications". In Proc. World Academy of Science, Engineering and Technology, 60, pp. 921-930.

- [20]. Smith, K. C. andSedra, A. S. (1968). "The current conveyor—A new circuit building block". In Proc. IEEE, 56( 8), pp.1368–1369.

- [21]. Sedra, A.S. and Smith, K. C. (1970). "A second generation current conveyor and its applications". IEEE Tran. Circuit Theory, 17(1), pp.132–134.

- [22]. Wilson, B. (1989). "Universal conveyor instrumentation amplifier". Elect. Lett. 25(7), pp. 470–471.

- [23]. Maheshwari, S., andVerma, R. (2012). "Electronically Tunable Sinusoidal Oscillator Circuit". Active and Passive Electronic Components (apec), Hindawi Publications, doi:10.1155/2012/719376.

- [24]. Narendra, S., De, V., Borkar, S., Antoniadis, D., andChandrakasan, A. (2004)." Full-chip subthreshold leakage power prediction and reduction techniques for sub-0.18-um CMOS". IEEE J. Solid-State Circuits, 39 (3), pp. 501–510.

- [25]. Ferri, G. &Guerrin, N. C. (2003). "Low-voltage Low-power CMOS current conveyors", 2nd ed., Kluwer Academic Publishers: New York press.

#### Authors Profile

MohdAjmalKafeel received B. Tech and M.Tech from ZH College of Engineering & Technology, Aligarh Muslim University (AMU) in the year 1998 and 2005 respectively. He is currently pursuing PhD in Electronics Engineering, from Department. Of Electronics Engineering,

AMU, Aligarh. His Research areas include VLSI Design of Devices and Circuits and Digital Systems. He is currently working as Assistant Professor in Electronics Engineering at University Women's Polytechnic, AMU, Aligarh.

Mohammad Zulqarnain received the B.Tech.andM.Tech degree in Electronics Engineering from Aligarh Muslim University, Aligarh, India,in 2012 and 2015 respectively. His current research interests include the design of subthreshold circuits, neuromorphic and

memristivecircuits.

**Prof. Hasan** has been working as a full Professor since March, 2005. He completed his **PhD** from the University ofEdinburgh, UK on a Commonwealth Scholarship in the area of "Low Power

Architectures for Signal Processing and Communications". He also worked as a Visiting Researcher on his own Royal Academy of Engineering, UK funded project on "Low Power FPGA' in the same University. He has published more than 132 papers in refereed journals and conferences with more than 400 citations. This also includes ten IEEE Transactions and 40 other journal publications.

Muhmmad Shah Alam obtained his B.Sc. Engineering (Electronics & Communication Engineering) and M.Sc. Engineering (Electronics & Communication Engineering) degrees from Aligarh Muslim University in year 1988 and 1991, respectively. He was

awarded Queen's research fellowship for carrying out research at the Queen's University of Belfast (UK) from where he obtained his **Ph.D**. degree in Electronics Engineering in year 2002. He worked as a visiting scientist at Nano-Technology center at Queen's University of Belfast (QUB) during 2004-05 under Royal Society (London) funded scheme. He completed his post-doctoral study in the area of nano-electronics under Commonwealth Fellowship Program in the year 2010.