# A New Switched Capacitor Inverter Topology with Boost Facility

M.Chenchaiah<sup>1</sup>, Dr.B.Mouli Chandra<sup>2</sup>

<sup>1</sup>PG Scholar, <sup>2</sup>Associate. Professor,

<sup>1, 2</sup> Department of EEE, QIS College of Engineering & Technology, Ongole, AP, India,

Email: mallela.chenchaiah@gmail.com. bmoulichandra@gmail.com.

# **ABSTRACT:**

A new switched capacitor inverter topology suitable for photovoltaic applications is proposed in this paper. The inverter is capable of boosting up low voltage DC in to high voltage DC and then invert it to the required voltage level with high quality in single stage. The proposed inverter has a special extended structure, which minimizes the number of components and devices when compared to the conventional multilevel inverter topology. Further some of the switches in the topology operate in the low frequency and this result in reduction in switching losses there by increasing the efficiency. The inverter is switched by the means of

In recent days, multilevel inverter (MLIs) has grown to be an attractive topic among researches, who work in the area of which includes Renewable energy integration and high power converters etc. MLIs are capable of generating nearly sinusoidal waveforms, which improves the problem of power quality. Principally, MLIs produces a high quality AC voltage waveform from a several DC voltage sources. In general MLIs are classified into three different categories they are: Cascaded H bridge inverter topology, diode clamped inverter topology and capacitor clamped inverter topology.

The main disadvantage of diode clamped inverter topology is that it shares unequal voltage between series connected capacitors and also it requires many diodes to produce more number of voltage levels at the output. Some of the advanced diode clamped inverter topologies are presented in [1]-[4]. In those topologies diodes are replaced with active devices, but this result in increased conduction losses because of high total conduction voltage at zero vectors. A cascaded MLI has many H bridges connected in series. Each H Bridge requires a separated DC source. If the magnitude of DC sources of all the H

level shifting carrier based Pulse Width Modulation (PWM) methodology which maintains the capacitor voltages at a balanced level. The proposed topology operation is verified through simulation in MATLAB/SIMULINK and the results are presented. A detailed comparison of the proposed inverter with other inverter proposed in the literature is also presented.

#### **KEY WORDS:**

Switched Capacitor, Multilevel inverter, Voltage balancing in capacitors, Level shifted PWM technique.

# INTRODUCTION

Bridge is equal then the configuration is called as symmetrical configuration, where as if the magnitudes of DC sources are different then the configuration is called as Asymmetrical configuration. Asymmetrical configuration can generate more number of levels at the load when compared to Symmetrical configuration. But controlling the asymmetrical configuration is highly complicated when compared to symmetrical configuration. Further in both the configurations the number of DC source and the number of devices is higher for higher levels.

Photovoltaic (PV) applications, generally requires a DC-DC boost converter to step up a low DC voltage into a high DC voltage as required by the grid or the standalone load. This high DC voltage is again inverted in to AC voltage using a high quality MLI. Thus it requires two stages of conversion. First stage is to step up the low voltage DC of PV in to high voltage and the second stage is to convert the high DC voltage generated from first stage into AC voltage of high quality. Thus this two stage conversion increases the system complexity and reduces the efficiency of the system.

This paper proposes a new extendable capacitor clamped MLI using switched capacitor topology. Further the proposed inverter uses a level shifting carrier based Pulse Width Modulation method to trigger the devices of the inverter. The main advantage of the proposed inverter is that the number of components used is minimized due to its combined structure. Further the proposed inverter can be extended to any required number of levels just by adding four switches and four capacitors. The remaining part of the paper is organized as follows. Topology derivation is derived in section III. In section III PWM topology for capacitor voltage balancing is dealt in detail. Finally, simulation results are detailed in Section III.

# PROPOSED TOPOLOGY

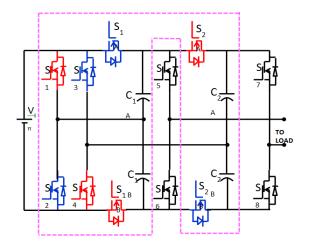

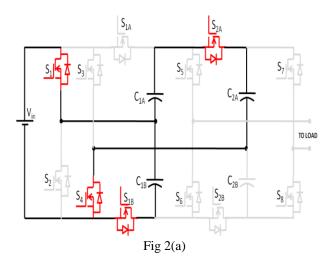

The proposed topology is shown in figure 1, which consists of conventional H bridge and a switched capacitor network connected to the front end of the conventional H bridge. The switched capacitor topology (SCT) is proposed in [5]-[8] as shown in figure 1 in dotted structure. The SCT has four capacitors and eight power devices. Switches  $S_1$ ,  $S_4$ ,  $S_{1B}$ ,  $S_{2A}$  are named as  $S_P$  switches and  $S_2$ ,  $S_3$ ,  $S_{1A}$ ,  $S_{2B}$  are named as  $S_N$  switches. The operation of the proposed inverter has two states. In state A  $S_P$  switches are turned ON and in state B  $S_N$  switches are turned ON as shown in figure 2(a) and 2(b) respectively.

Fig 1. Proposed Inverter

Fig 2 (a) Conduction Diagram for State A (b) Conduction Diagram for State B

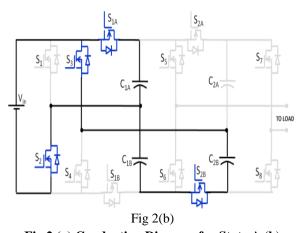

There are five modes of operation of the proposed inverter to generated five levels. Operating modes of the proposed inverter are shown in figure 3 and explanations are given for each mode.

Mode 1: Figure 3(a) and figure 3(b) shows the mode 1 operation, in mode 1  $S_P$  group switches and  $S_5$  and  $S_7$  switches are in ON condition and the other switches are in OFF condition. Output voltage across the load is 0 volts since the input voltage is not connected to the load. Capacitor  $C_1$  and  $C_{2A}$  are in parallel to each other. Similarly when switches of  $S_N$  group and  $S_6$  and  $S_8$  are in ON condition a similar situation exists.

Fig 3. Modes of operation of the proposed inverter.

Mode 2: In Fig. 3(c) and 3(d), corresponds to mode 2, voltage value of  $2V_{in}$ can be obtained from the proposed converter. One operation state is that switches group  $S_P$ , switches  $S_6$ ,  $S_8$  are turned ON and other switches are turned OFF, capacitors  $C_1$  and  $C_{2a}$  are in parallel connection, inverter has the output voltage of  $C_{2b}$ , as shown in Fig. 3(c). Fig. 3(d) shows another operation state with switches group  $S_N$ , switches  $S_5$ ,  $S_8$  turned ON and other switches turned OFF, capacitors  $C_1$  and  $C_{2b}$  are in parallel connection, the inverter produces the voltage of  $C_{2b}$ .

Mode 3: In Fig. 3(e), corresponds to the mode 3 operation in this, switches group  $S_P$ , switches  $S_5$ ,  $S_8$  become on-state, capacitors  $C_1$  and  $C_{2a}$  are parallel connection, the inverter outputs the summation voltage of capacitor  $C_{2a}$  and  $C_2$ .

Mode 4: In Fig. 3(f) and 3(g) corresponds to the mode 4 operation, switches group  $S_P$ , switches  $S_6$ ,  $S_7$  are turned ON and capacitors  $C_1$  and  $C_{2a}$  are in parallel connection, the inverter outputs the reverse voltage of  $C_{2A}$  with value of  $-V_{in}$ . In Fig. 3(g), switches group  $S_N$ , switches  $S_5$ ,  $S_7$  conduct and capacitors  $C_1$  and  $C_{2B}$  are in parallel connection, the inverter outputs the reverse voltage of  $C_{2A}$  with value of  $-2V_{in}$ .

Mode 5: In Fig. 3(h), corresponds to mode 5 operation, switch group  $S_N$ , switches  $S_6$ ,  $S_7$  become on-state and capacitors  $C_1$  and  $C_{2B}$  are in parallel connection, the inverter produces the reverse voltage of  $C_{2A}$  and  $C_{2B}$  with value of  $-4V_{in}$ .

# PERFORMANCE COMPARISION

The performance of the proposed inverter is compared in terms of active devices, diodes, capacitors, front end boost conversion, voltage stress, switching frequency, capacitor voltage balance control and number of DC sources with that of other similar type of inverters available in the literature. Table 1 shows a detailed comparison.

|                                      | Five Level Inverter |                     |                    |                                                                                           |  |  |  |  |

|--------------------------------------|---------------------|---------------------|--------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

|                                      | Diode               | Capacitor           | Cascaded           | Proposed Inverter                                                                         |  |  |  |  |

|                                      | Clamped             | Clamped             | H bridge           |                                                                                           |  |  |  |  |

| Active Switches                      | 8                   | 8                   | 8                  | 12                                                                                        |  |  |  |  |

| Diodes                               | 12                  | 0                   | 0                  | 0                                                                                         |  |  |  |  |

| Capacitors                           | 4                   | 10                  | 2                  | 4                                                                                         |  |  |  |  |

| Front End Boost Conversion           | Needed              | Needed              | Needed             | Not Needed                                                                                |  |  |  |  |

| Voltage Stress                       | 0.25 U <sub>B</sub> | 0.25 U <sub>B</sub> | 0.5 U <sub>B</sub> | ✓ 0.25 U <sub>B</sub> (8 Nos)<br>✓ 0.5 U <sub>B</sub> (2 Nos)<br>✓ U <sub>B</sub> (2 Nos) |  |  |  |  |

| Switching Frequency                  | f <sub>c</sub>      | fc                  | fc                 | f <sub>c</sub> (4 switches)<br>f <sub>l</sub> (4 switches)                                |  |  |  |  |

| Capacitor Voltage Balance<br>Control | Difficult [9]       | Difficult[10]       | Difficult          | Easy                                                                                      |  |  |  |  |

| Number of DC sources                 | 1                   | 1                   | 2                  | 1                                                                                         |  |  |  |  |

**Table 1: Performance Comparison**

# **SWITCHING LOGIC**

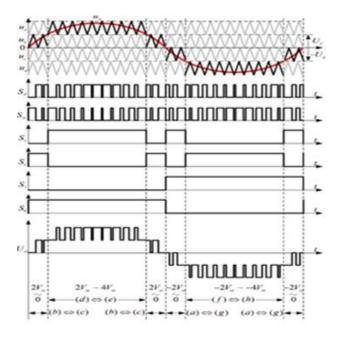

The switching logic of the proposed inverter is shown in figure 4. It has four level shifted carrier waveforms compared with the sinusoidal reference waveform.

From figure 4 it can be seen that four switches operates at low frequency which reduces the switching losses there by increasing the efficiency. Table 2 shows the switching logic of the proposed inverter in a simplified form.

| Condition for<br>Modulation and<br>Carrier Wave |                                 | Switching States |             |                |                |                       |                |  |

|-------------------------------------------------|---------------------------------|------------------|-------------|----------------|----------------|-----------------------|----------------|--|

|                                                 |                                 | Sp               | $S_{\rm N}$ | S <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> |  |

| U <sub>S</sub> >=                               | $U_{S} \ge U_{A}$               | 1                | 0           | 1              | 0              | 0                     | 1              |  |

|                                                 | $U_S < U_A$                     | 0                | 1           |                |                |                       |                |  |

| 0<br><=Us<br>< Uc                               | $U_S >= U_B$                    | 1                | 0           | 0              | 1              | 0                     | 1              |  |

|                                                 | $U_S < U_B$                     | 0                | 1           |                |                |                       |                |  |

| - Uc                                            | $U_S >= U_C$                    | 1                | 0           |                |                |                       |                |  |

| <=U <sub>S</sub><br>< 0                         | U <sub>S</sub> < U <sub>C</sub> | 0                | 1           | 1              | 0              | 1                     | 0              |  |

| U <sub>S</sub> <-                               | $U_S >= U_D$                    | 1                | 0           | 0              | 1              | 1                     | 0              |  |

| Uc                                              | $U_S < U_D$                     | 0                | 1           |                | _              | _                     |                |  |

Table 2: Switching Logic of the proposed inverter.

Figure 4 Switching logic of the proposed inverter.

# SIMULATION RESULTS

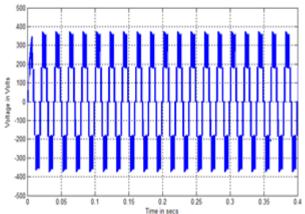

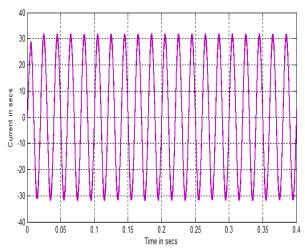

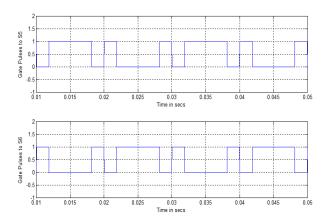

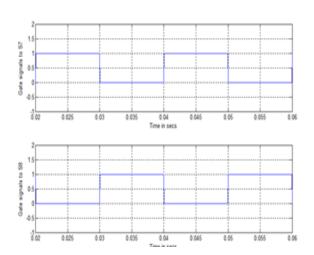

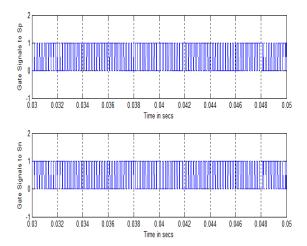

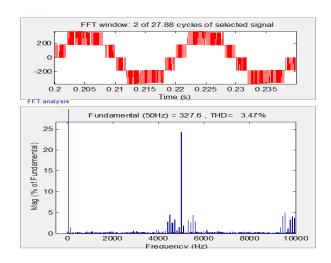

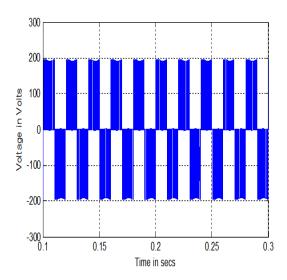

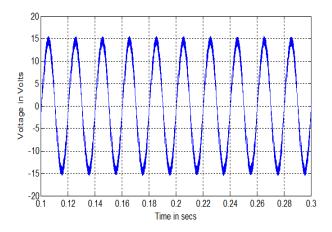

The proposed inverter is simulated using MATLAB/SIMULINK software and the results are presented in this section. The proposed inverter is fed from dc voltage of 100 V and the voltage is boosted to nearly 400 V peak as shown in figure 5. The proposed inverter can be used for high power applications as shown in figure 6 as the current delivered to the load is nearly 30 A peak. Figure 7 shows the switching patterns of the S<sub>P</sub> and S<sub>N</sub> switches. Similarly Figure 8 shows the switching patterns of the switches  $S_5$  and  $S_6$ . Finally the switching patterns of the switches S<sub>7</sub> and S<sub>8</sub> are shown in figure 9.

Fig 5. Load Voltage Waveform

Fig 6. Load Current Waveform

# International Journal of Advanced Information Science and Technology (IJAIST) ISSN: 2319:2682 Vol.6, No.11, November 2017 DOI:10.15693/ijaist/2017.v6i11.157-162

Fig 7 Switching pulses for S<sub>P</sub> and S<sub>N</sub> Switches.

Fig 8Switching pulses for S<sub>5</sub> and S<sub>6</sub> Switches.

Fig 9 Switching pulses for S7 and S8 Switches

Fig 10 Output Voltage THD

The total harmonic distortion of the inverter when it is operating in full load is shown in figure 10. The modulation index of the proposed inverter is varied from 0 to 1 and the performance of the inverter is studied. It is found that the number of levels reduces to three when the modulation index is reduced. The voltage waveform of the reduced modulation index is shown in figure 11. Figure 12 shows the current waveform for modulation index of 0.5. It is found that the total harmonic distortion is less than 5% which is the prescribed limit of IEEE standards.

Fig 11 Load voltage with Modulation index = 0.5

# International Journal of Advanced Information Science and Technology (IJAIST) ISSN: 2319:2682 Vol.6, No.11, November 2017 DOI:10.15693/ijaist/2017.v6i11.157-162

Fig 12 Load Current with Modulation index = 0.5

# **CONCLUSION**

A novel single phase five level boost inverter is presented which is suitable for renewable energy applications. Some of the switches of the proposed inverter operate in low frequency which makes the inverter to operate at high efficiency. The proposed inverter uses minimum number of switching devices when compared to the other inverters proposed in the literature. Simulation results are presented for different modulation indexes.

# **REFERENCES**

- Rodriguez, J., Lai, J. S., &Peng, F. Z. (2002). Multilevel inverters: a survey of topologies, controls, and applications. *IEEE Transactions on industrial* electronics, 49(4), 724-738.

- Venkatesan, M., Rajeswari, R., Kaliyamoorthy, M., &Srithar, M. (2017). Transient and Steady State Analysis of Modified Three Phase Multilevel Inverter for Photovoltaic System. *International Journal of Power Electronics and Drive* Systems (IJPEDS), 8(1).

- Ponnusamy, S. R., Subramaniam, M., Irudayaraj, G. C. R., &Mylsamy, K. An Improved Switching Topology for Single Phase Multilevel Inverter with Capacitor Voltage Balancing Technique.

- Boopathy, C. P., &Kaliamoorthy, M. (2016). A Novel Asymmetrical Single-Phase Multilevel Inverter Suitable for Hybrid Renewable Energy Sources. *Circuits and Systems*, 7(06), 932.

- Boopathy, C. P., &Kaliamoorthy, M. (2016). A Modified Asymmetrical Single-Phase Multilevel Inverter Topology for

- Enhanced Power Quality. *Middle-East Journal of Scientific Research*, 24(4), 1004-1015.

- Venkatesan, M., Rajeshwari, R., Deverajan, N., &Kaliyamoorthy, M. (2016). Comparative Study of Three Phase Grid Connected Photovoltaic Inverter Using PI and Fuzzy Logic Controller with Switching Losses Calculation. International Journal of Power Electronics and Drive Systems, 7(2), 543.

- Raj, I. G. C., Kaliamoorthy, M., Rajasekaran, V., &Sekar, R. M. (2015). Single-Phase Cascaded Grid Connected Multilevel Inverter for Interfacing Renewable Energy Sources With Microgrid. *Journal of Solar Energy Engineering*, 137(5), 051004.

- Kaliamoorthy, M., Rajasekaran, V., Raj, I. G. C., & Raj, L. H.

T. (2014). Generalised hybrid switching topology for a single-phase modular multilevel inverter. *IET Power Electronics*, 7(10), 2472-2485.+

- Mylsamy, K., Vairamani, R., Irudayaraj, G. C. R., & Lawrence, H. T. R. (2014). Experimental validation of a cascaded single phase H-bridge inverter with a simplified switching algorithm. *Journal of Power Electronics*, 14(3), 507-518.

- Kaliamoorthy, M., Himavathi, S., &Muthuramalingam, A. (2006, December). DSP based implementation of high performance flux estimators for speed sensorless induction motor drives using TMS320F2812. In *Power Electronics*, 2006. IICPE 2006. India International Conference on (pp. 104-109). IEEE.