International Journal of Advanced Information Science and Technology (IJAIST) ISSN: 2319:268 Vol.2, No.4, April 2013 DOI:10.15693/ijaist/2013.v2i4.139-142

## Low Swing In Clock Pair Shaired Implicit Pulsed Flip-Flop

<sup>1</sup>Praveen C.S,<sup>2</sup>Ananth V.M <sup>1</sup>PG Scholar, <sup>2</sup>Assistant Professor, Department of ECE, Karpagam University, Coimbatore-641021, Tamilnadu, India

Abstract— Power consumption is a major bottleneck of system performance a large portion of the on chip power is consumed by the clock system which is made of the clock distribution network and flop-flops. An effective way to reduce capacity of the clock load by minimizing number of clocked transistors .The proposed low-swing in clock pair shared implicit pulsed flip-flop (LS-CPSIPFF) operates with a low-swing sinusoidal clock through the utilization of reduced swing inverters at the clock port. The LS-CPSIPFF enables 6.5% reduction in power compared to the full swing flip-flop with 19% area overhead. The LS-DCCFF has 870 ps longer data to output delay as compared to the full-swing flip-flop at the same setup time for a 100 MHz sinusoidal clock.

*Index Terms*—Delay, flip-flop, low-swing, power, resonant clocking, low-swing in clock pair shared implicit pulsed flip-flop (LS-CPSIPFF)

### I. INTRODUCTION

Due to the increasing demand on portable applications and the increased cost of cooling, lowpower has become a crucial design objective. Resonant clocking has demonstrated significant advantages in terms of power savings compared to conventional square-wave clocking resonant clock generators with programmable driver and reference pulses, none of them have addressed the need to estimate the required driver strength at an early stage of the design. Estimation the required driving capability of the driver in the resonant clock generator[1].

The system on chip (SoC) design is integrating hundreds of millions of transistors on one chip, whereas packaging and cooling only have a limited ability to remove the excess heat. All of these results in power consumption being the bottleneck in achieving high performance and it is listed as one of the top three challenges in ITRS 2008. The clock system, which consists of the clock distribution network and sequential elements (flip-flops and latches), is one of the most power consuming components in a VLSI system [1], [2]. It accounts for 30% to 60% of the total power dissipation in a system [1]. As a result, reducing the power consumed by flip-flops will have a deep impact on the total power consumed. A large portion of the on chip power is consumed by the clock drivers. Caution must be paid to reduce clock load when designing a clocking system. Resonant clocking enables the generation of clock signals with reduced power consumption. The traditional approach for LC resonant CDNs is to use the LC tank to drive the global clock distribution while the local square clock is being delivered through conventional buffers. However, around 66% of clock power is being dissipated in the last buffer stage driving the flip-flops [4], leading to minor power savings in LC globally-resonant locally-square CDNs. In order to achieve maximum power savings, the LC tank should drive the entire clock network

(both global and local) without using intermediate buffers. This would require designing, modifying and understanding flip-flop performance with the sinusoidal clock signal generated in LC resonant networks.

In this paper, we introduce a low-swing differential conditional capturing flip-flop (LS-DCCFF) for use in low-swing LC resonant CDNs.

As far as the authors know, this is the first application of low-swing clocking to LC resonant CDNs. In our approach, no additional power supply is required to achieve low-swing clocking. We have characterized a frequency dependent delay associated with driving the pulsed flip-flop with a low-swing sinusoidal clock.

Power consumption is determined by several factors including frequency f, supply voltage v, data activity, capacitance c, leakage, and short circuit current.[3]

$$P = P_{dynamic} + P_{short-circuit} + P_{leakage}$$

(1.1)

In the above equation, dynamic power  $P_{dynamic}$  is also called the switching power,

$p_{dynamic} = c.V_{DD}.V_{P.}f$  (1.2) In the above equation c denotes the output capacitance, vdd is the supply voltage,  $v_p$  is the peak voltage stored on that capacitor and f denotes the frequency.  $P_{short-circuit}$  is the short circuit power which is caused by the finite rise and fall time of input signals, resulting in both the pull up network and pull down network to be ON for a short while

$$P_{shortcircuit} = I_{shortcircuit}. V_{DD}$$

(1.3)

$P_{leakage}$  is the leakage power. When the supply voltage scaling down, the threshold voltage also decreases to maintain performance . However, this leads to the exponential growth of the subthreshold leakage current. Sub threshold leakage is the dominant leakage now.

$$P_{\text{leakage}} = I_{\text{leakage}} V_{\text{DD}}$$

(1.4)

Based on these factors, there are various ways to lower the power Consumption. They are 1) Double Edge Triggering 2) low swing voltage 3) switching activity 4) Reducing short circuit power 5) Reducing leakage power 6) Reducing capacity of clock load [5]. In this paper we proposed first two techniques to reduce the amount of power consumption in differential conditional capturing flip-flop. To execute low swing voltage we proposed low swing inverters by which the peak voltage of input sinusoidal waveform is reduced to (Vdd-Vtp).

The remainder of this paper is organized as follows. A description of the proposed LS-DCCFF and a characterization of the delay associated with LC low-swing clocking are presented in Section II. Section III describes the test chip. Section IV includes simulation and measurement results obtained. The conclusion of this paper is provided in Section V.

### II. LOW-SWING LC RESONANT CLOCKING

## A)LS-CPSIPFF:

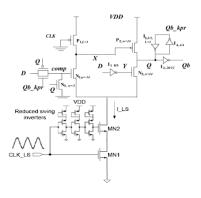

Fig. 2.1 shows the proposed LS-DCCFF. Conditional capturing flip-flop is used to avoid unwanted internal switching activity in the internal nodes of the flip-flop. As shown in Fig. 2.1, reduced swing inverters similar are used at the node fed by the low-swing sinusoidal clock signal. This is done to reduce the short circuit power. To operate the MOSFET in saturation region drain to source voltage( $v_{ds}$ ) should be greater than difference of gate to source voltage and threshold voltage.

$$V_{ds} \ge V_{gs} - V_t$$

(in saturation) (2.1)

The load pmos transistor in the reduced swing inverters is always in saturation since  $V_{gs} = V_{ds}$ . It lowers the voltage at the source of the second

pMOS in each inverter to approximately  $V_{DD}$ - $V_{tp}$  [7]. The peak voltage for the low swing clock was chosen to be equal to 0.65V since  $V_{DD}$  =1V and threshold voltage of pMOS transistor is approximately -0.34V.

Fig 2.1 LSCPSIPFF

# B. Delay Associated With Low swing LC Resonant Clocking:

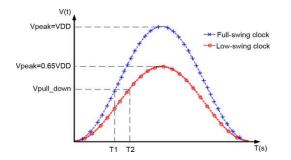

Resonant clock signal is applied to transistor MN1 and low swing sinusoidal clock signal is applied to MN2.  $V_{pulldown}$  is the voltage level at which transistors MN1 and MN2 turned on by which pull down node SET/RESET to lower voltage level required to trigger the NAND latch. From Fig.2.2 we can able to see that there is a time difference between full swing and low swing sinusoidal clock to reach  $V_{pulldown}$ . Thus low swing sinusoidal clock experiences longer data as compared to full swing.

In the following, an analysis is conducted to estimate the delay in reaching  $V_{pulldown}$  for low swing resonant clock signal. Let the full- and low-swing clock signals be given by the following equations:

$$V(t)_{\text{fullswing}} = \frac{1}{2}VDD \sin\left(2\pi fT - \frac{\pi}{2}\right) + \frac{1}{2}VDD \quad (2.2)$$

$V(t)_{\text{lowswing}} = \frac{0.65}{2} VDDsin\left(2\pi fT - \frac{\pi}{2}\right) + \frac{1}{2} VDD (2.3)$ where f is the clock frequency, V<sub>DD</sub> and 0.65V<sub>DD</sub> are the peak voltage for full-swing and low swing sinusoidal clock signals respectively. Referring to Fig 2.2 and substituting the value

$$V_{\text{pulldown}} = \frac{1}{2} VDDsin\left(2\pi fT1 - \frac{\pi}{2}\right) + \frac{1}{2} VDD \qquad (2.4)$$

From which

$$T_{1} = \frac{1}{2\pi f} \left( \sin^{-1} \left( \frac{2 \, V p \, u \, l \, d \, o \, wn}{V \, D \, D} - 1 \right) + \frac{\pi}{2} \right)$$

(2.5)

Fig.2.2. Delay between the low and full-swing resonant clock signals to reach  $V_{pull-down}$

Using the same approach for low swing clock signal

$$T_2 = \frac{1}{2\pi f} \left( \sin^{-1} \left( \frac{2 \, V pull down}{0.65 \, V DD} - 1 \right) + \frac{\pi}{2} \right)$$

(2.6)

The time difference between two clock signal to reach  $V_{pulldown}$  between low and full-swing flip-flops is given by,

$$T_{2}-T_{1}=\frac{1}{2\pi f}\left(\sin^{-1}\left(\frac{2Vpulldown}{0.65VDD}-1\right)-\sin^{-1}\left(\frac{2Vpulldown}{VDD}-1\right)\right) \quad (2.7)$$

The above equation gives the delay between the full and low swing flip-flops. It illustrates that this delay is inversely proportional to clock frequency i.e at higher frequencies, the delay decreases.

### C) Power

The power dissipation of the resonant clock network is given by following equation:

$$P_{\text{resonant\_clock}} = \frac{Rclk}{2} \left( \pi f V peak (Cclk + \alpha NC_{\text{FF}}) \right)^2 \quad (2.8)$$

Where  $R_{clk}$  and  $C_{clk}$  are the clock capacitance and resistance as seen by the driver ,f and Vpeak are the frequency and peak voltage of generated clock signal , $C_{FF}$ is the loading capacitance of the flip-flop, N is the number of flip-flops and  $\alpha$  is the factor by which the loading capacitance of the flip-flop connected at the clock leaves is reflected to the driver side . The above equation illustrates that generating a low swing clock signal with  $V_{peak} = 0.65 V_{DD}$ results in around 58% power reduction in clock network.

### IV. PERFORMANCE ANALYSIS

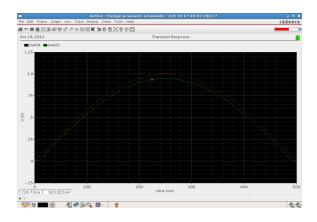

The LS-DCCFF enables 6.5% reduction in power compared to the full-swing flip-flop due to low swing by which peak voltage of input sinusoidal wave is reduced to  $0.65V_{DD}$  and also it results in 58% power reduction in clock network. The output of full swing clock and low swing clock is shown in Fig.3.1. In Fig 3.1 red color swing represent the full swing whereas green color swing represent the low swing resonant clock signals. It is clear that low swing resonant clock signal reduces the peak voltage of input signal and thereby reducing the power consumption in DCCFF.

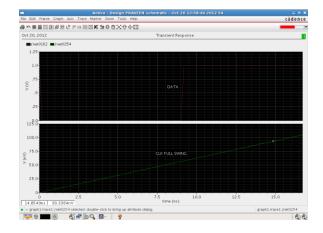

The original input data (D) and full swing input is shown in Fig3.2. The delay associated with full-swing and low swing LC resonant clocking scheme output is shown in Fig,3.3

Fig 3,1. Low-swing (green) and full-swing (Red) resonant clock signal

Fig 3.3 Delay associated with full-swing and low swing

International Journal of Advanced Information Science and Technology (IJAIST)ISSN: 2319:268Vol.2, No.4, April 2013DOI:10.15693/ijaist/2013.v2i4.139-142

Fig 3.4 Input of D and Output of Q in CPSIPFF

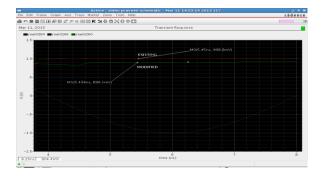

Fig 3.5 output of CPSIPFF existing and modified TABLE I AREA AND POWER COMPARISON BETWEEN FULL- AND LOW-SWING CLOCKING

| Contents                | LSCPSIPFF |

|-------------------------|-----------|

| Area (µm <sup>2</sup> ) | 43        |

| % increase in area      | 19        |

| compared to full swing  |           |

| Power (µW)              | 4.58      |

| % decrease in power     | 17.5      |

| compared to full swing  |           |

### V. CONCLUSION

We have proposed a low-swing sinusoidally clocked flip-flop to obtain further power reduction in LC resonant CDNs. Low-swing resonant clocking in pulsed flip-flops results in a delayed flip-flop response. Theoretical analysis has been performed and the delay associated with low-swing sinusoidal clocking was characterized.

## VI. REFERENCES

[1] Peiyi Zhao, Jason Mc Neely, Weidong Kuang, Nan Wang and Zhog feng Wang, "Design of Sequential Elements for Low Power Clocking System,", IEEE Trans. Very Large Scale Integr. VOL. 19, NO. 5, MAY 2011 [2] Seyed E. Esmaeili, Asim J. Al-Kahlili, and Glenn E. R. Cowan, "Low-SwingDifferential Conditional Capturing Flip-Flop for LC Resonant Clock Distribution Networks," IEEE Trans. Very Large Scale Integr. (VLSI) SYSTEMS, VOL. 20, NO. 8, AUGUST 2012

[3] V. F. Pavlidis, I. Savidis, and E. G. Friedman, "Clock distribution networks in 3-D integrated systems," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 10.1109/TVLSI.2010.2073724.

[4] A. J. Drake, K. J. Nowka, T. Y. Nguyen, J. L. Burns, and R. B. Brown, "Resonant clocking using distributed parasitic capacitance," IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1520–1528, Sep. 2004.

[5] C. Kim and S. M. Kang, "A low-swing clock double-edge triggered flip-flop," in Proc. Symp. VLSI Circuits, 2001, pp. 183–186.

[6] F. H. A. Asgari and M. Sachdev, "A lowpower reduced swing global clocking methodology," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 5, pp. 538–545, May 2004.

[7] J. Pangjun and S. S. Sapatnekar, "Low-power clock distribution using multiple voltages and reduced swings," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 3, pp. 309–318, Jun. 2002.

[8] H. Mahmoodi, V. Tirumalashetty, M. Cooke, and K. Roy, "Ultra lowpower clocking scheme using energy recovery and clock gating," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no. 1, pp. 33–44,Jan. 2009.

[9] S. E. Esmaeili, A. J. Al-Khalili, and G. E. R. Cowan, "Estimating required driver strength in the resonant clock generator," in *Proc. IEEE Asia Pacific Conf. Circuits Syst.*, 2010, pp. 927–930.

[10] S. E. Esmaeili, A. J. Al-Khalili, and G. E. R. Cowan, "Dual-edge triggered sense amplifier flipflop for resonant clock distribution networks," *IET Comput. Digit. Tech.*, vol. 4, no. 6, pp. 499–514, Nov.2010.

[11] Z. Xu and K. L. Shepard, "Design and analysis of actively-deskewed resonant clock network," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 558–568, Feb. 2009