## Asynchrobatic Power-Gated Logic With Pcr Implementation

Ms.K.R.S.Deepa<sup>1,</sup> Ms.G.Vinothini<sup>2</sup>, Ms.V.Suganyaa<sup>3</sup>, Prof.G.R.Mahendra Babu<sup>4</sup> <sup>1, 2, 3</sup>Master of Engineering (VLSI DESIGN), ECE, <sup>4</sup> Working as Associate Professor, ECE, Karpagam University, Coimbatore, Tamil Nadu, India.

Abstract- In this work, Asynchrobatic Powergated logic may be a novel low-power style vogue that mixes the energy saving edges of asynchronous logic and adiabatic logic to provide systems whose power dissipation is reduced. Every pipeline stage within the APL circuit is comprised of improved efficient charge recovery logic (IECRL) gates, which implement the logic perform of the stage, and a handshaking controller, that handles handclasp with the neighboring stages and provides power to the IECRL gate. With the PCR mechanism, a part of the charge on the output nodes of associate IECRL gate coming into the discharge part is reused to charge the output nodes of another IECRL gate on the brink of value, reducing the energy dissipation needed to complete the analysis of associate IECRL gate. Moreover, APL-PCR adopts associate increased C-element, known as C-element, in its handshaking controllers specified associate ECRL gate in AFPL-PCR will enter the sleep mode early once its output has been received by the downstream pipeline stage.

*Keywords:* Asynchrobatic Logic, Power dissipation, partial charge reuse, Handshaking

#### **1. Introduction**

As the feature size continues to shrink and additionally the corresponding semiconductor density can increase, power dissipation has become an important concern in nanoscale CMOS VLSI vogue. Power dissipation in CMOS circuits is classified into dynamic dissipation and static dissipation. Dynamic power is that the facility dissipated once the device is active, and static power is that the facility dissipated once the device is powered up but no signals are changing their values.

Relying upon the appliance, there are numerous ways in which is also accustomed trim the power consumption of VLSI circuits, these can vary from low-level measures based upon elementary physics, like using a lower power offer voltage or victimization high threshold voltage transistors; to high-level measures like clock-gating or power-down modes. The two that meant this investigation were asynchronous logic and adiabatic logic. These a pair of technologies area unit combined to create Asynchronous, adiabatic Logic methodology, referred to as Asynchrobatic Logic. The name comes as a concatenation and shortening of Asynchronous, and adiabatic Logic.

One of the properties of asynchronous systems that build them helpful within the applications are that circuits embrace a integral inability to variations in power offer voltage, with a lower voltage leading to slower operation instead of the useful failures that might be seen if ancient synchronous systems were used. Another major advantage is that the undeniable fact that once associate asynchronous system is idle there will be no ticking clock signals. But in synchronous systems, these clock signals are propagated throughout the complete system and convert energy to heat, typically while not play acting any helpful computations.

Adiabatic logic may be a newer space of low-power analysis. The low-power advantage of adiabatic logic is that energy may be recycled by being kept and reused, therefore reducing the number of energy drawn directly from the facility offer. There are different low-power consequences of exploitation sure realizations of adiabatic logic, however these are implementation specific instead of being directly as a result of the reversible nature of the logic.

The two analysis areas represented higher than each had a unique set of low-power edges that they might wake circuit style, and Asynchrobatic Logic was born out of the novel plan to try to search out how to unify the low-power edges from these fields. IECRL is extremely almost like ECRL, however with the addition of a try of crosscoupled NMOS devices to relinquish a more robust association to ground once inputs have had their charge recovered.

Moreover, the partial charge recycle (PCR) mechanism will be combined with APL to scale back the energy dissipation needed to finish the analysis of a logic block.

The remainder of this paper is organized as follows: In Section 2, we have provided a structure of APL pipeline and describe the functional block and handshake controllers employed in the APL pipeline. Section 3, we have a provided the operations and functional blocks of

PCR mechanism and also the enhanced C\*element. Section 4, show the simulation results of our project and discussed regarding them. Section 5, is dealing with conclusion and future work of our project.

#### 2. APL

#### 2.1. Overview

In this chapter, the basic concepts of adiabatic logic are going to be introduced. "Adiabatic" could be a term of Greek origin that has spent most of its history related to classical thermodynamics. It refers to a system during which a transition happens while not energy (usually within the type of heat) being either lost to or gained from the system. Within the context of electronic systems, instead of heat, electronic charge is preserved. Thus, a perfect adiabatic circuit would operate while not the loss or gain of electronic charge. Though associate earlier suggestion of the likelihood of energy recovery was created and declared "This energy might in theory be saved and reused".

The introduction to the present section details the etymology of the term "adiabatic logic". During this section, the underlying physics square measure thought-about. Due to the Second Law of thermodynamics, it is impracticable to utterly convert energy into helpful work. However, the term "Adiabatic Logic" is employed to explain logic families that logically operate while not losses. This additionally semiconductor diode to the thought of a system that might be operated haphazardly slowly specified its dissipation could asymptotically approach zero as its speed was reduced.

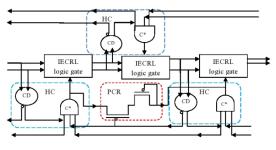

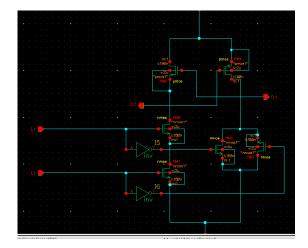

#### Fig 1: APL

The Asynchrobatic Power-gated Logic can be a method circuit that operates every asynchronously and adiabatically. Before this, natural process had occurred synchronously, any self-timed adiabatic circuits exclusively had applications as drivers, merely capable of repetition a signal, but not acting any operation upon it. Since asynchronous logic had been used with logic incapable of charge recovery or adiabatic operation.

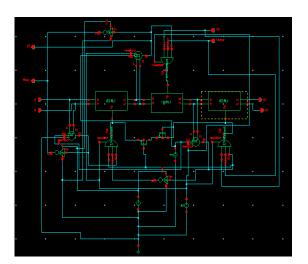

#### Fig 2: SCHEMATIC OF APL

The slowest of those is generally slowest method, lowest tolerable voltage and highest temperature. Outside of the qualified vary the circuits could fail owing to violating setup-time necessities, with data-arriving too late to be properly barred by a clock edge. This limits the voltage scaling that will be applied to a synchronous circuit. For each commonplace synchronous and commonplace asynchronous logic, the result of lowering the voltage can cut back the power-consumption.

Other low-power advantages is illustrated by wanting forward associate degreed considering an oversized Asynchrobatic system compared to associate degree equivalently massive asynchronous system and an equivalently large synchronous system. The shortage of a global clock is additionally a significant profit. Within the synchronous system, the ticking global clock would at minimum, reach a clock-gating component at the entry to every stage, and consequentially would waste energy. Within the asynchronous and Asynchrobatic systems, the inactive states area unit simply that, inactive, and intrinsically, with no switch occurring; solely run power are going to be consumed. Asynchronous logic is additional technologically mature than adiabatic logic.

#### 2.2. Functional blocks of APL

Over the last 20 years many alternative adiabatic or quasi-adiabatic logic families are valid to construct the practical blocks of APL. In this ECRL, IECRL, PFAL and EACRL are a number of the adiabatic logic families.

Efficient Charge Recovery Logic (ECRL) seems to own been severally discovered by Kramer, UN agency gave it the systematic name "2N-2P", ECRL and 2N-2P area unit identical, and area unit based mostly upon the quality CMOS family referred to as Differential Cascode Voltage Switch Logic (DCVSL) [4]. This structure uses combines of pull-down NMOS devices to judge functions (designated by the "2N") and a pair of cross-coupled PMOS devices (designated by the

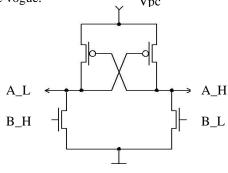

"2P") to carry state. It is often cited and has clearly been the inspiration for several different similar adiabatic logic families. Complete recovery of the power-clock is not doable through the PMOS devices; therefore it is still solely a quasi-adiabatic logic vogue. Vpc

Fig 3: An ECRL Buffer

ECRL [1] (also referred to as 2N-2P [5]) is predicated around a try of cross-coupled PMOS transistors. Their supply terminals area unit connected to the power-clock, and therefore the gate of everyone is connected to the drain of the opposite. These nodes kind the complementary output signals. The operation is evaluated by a series of pull-down NMOS devices. Within the original description, the property of the PMOS transistors bulk terminals was not specified. However, experimentation has shown that higher power performance is obtained by connecting the majority to the power-clock, because the powerclock is recovered to a lower voltage. This improvement is not while not value, because it introduces layout constraints that need the new nwells of every Asynchrobatic stage to be unbroken separated. One disadvantage of ECRL is that after the charge from the previous stage has been recovered from the gate of the NMOS devices, there's no pull-down path to ground. This has implications for noise condition. The power-clock drives the terminal labeled "Vpc". The dual-rail input try "A" and dual-rail output try is a unit shown with their high and low assertion levels indicated by the "A H" and "A L" suffixes.

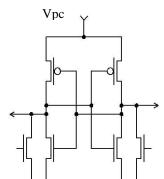

Improved Efficient Charge Recovery Logic (IECRL) was originally merely represented as associate "Adiabatic Logic Gate", consistently named by Kramer, and later known as Improved Efficient Charge Recovery Logic (IECRL). IECRL differs terribly slightly from the previous description by specifically exploitation the PMOS device to make a try of recovery diodes. IECRL is incredibly the same as ECRL, however with the addition of a pair of cross-coupled NMOS devices to grant an improved association to ground once inputs have had their charge recovered.

#### Fig 4: An IECRL Buffer

IECRL [6] (originally referred to as 2N-2N2P by Kramer et al. in [5], however 1st represented by Denker in [3] improves ECRL with the addition of a try of cross-coupled NMOS devices. This produces a logic family that's based mostly around a try of cross-coupled inverters, a structure that's just like the storage components during a Static RAM (SRAM). The cross-coupled NMOS devices area unit associate improvement over ECRL as a result of the supply a pull-down path to ground that continues to be even when the charge is recovered from the gates of the analysis FETs. However, owing to the 2 additional NMOS devices, it'll need a bigger space within which to be enforced. This figure uses identical naming and assertion level conventions because the ECRL circuit.

#### Fig 5: SCHEMATIC OF IECRL

Positive Feedback adiabatic Logic (PFAL) conjointly later known as PAL-2N. PFAL is incredibly the same as IECRL; however has its analysis tree connected between power-clock and outputs. It is able to do absolutely adiabatic operation once a recovery path is provided.

Efficient adiabatic Charge Recovery Logic (EACRL) features a pair of cross-coupled PMOS devices, and duplicate sets of analysis logic, one set is connected between ground and therefore the outputs, while the opposite is connected (with associate opposite assertion level) between the power-clock and therefore the outputs. Within the same manner as PFAL, it can also be created absolutely adiabatic once a recovery path is provided.

The data-path logic for Asynchrobatic Logic is designed in mere identical manner because it would be for adiabatic logic. A designer would be liberal to choose between a range of various adiabatic families together with, however not restricted to; Efficient Charge Recovery Logic (ECRL), Improved Efficient Charge Recovery Logic (IECRL), Positive Feedback adiabatic Logic (PFAL) or Efficient adiabatic Charge Recovery Logic (EACRL). The ECRL data-path showed a more-or-less mounted power consumption regardless of the quantity of change, though its power consumption did increase slightly because the change likelihood hyperbolic. This variation will possibly be attributed to the non-linear nature of associate ECRL circuit as a load on a SWC circuit inflicting the convergence voltages of the tank capacitors to vary, so moving the quantity of retrievable charge.

It's clearly evident that a 16-bit, ECRL Asynchrobatic Logic pipeline can forever be less power economical than constant asynchronous pipeline. However, for a 32-bit, ECRL Asynchrobatic Logic pipeline, it is seen that if quite seventieth of the bits (23 bits) modification, then the Asynchrobatic Logic implementation are the lot of Efficient.

ECRL, IECRL and PFAL area unit 3 of the only adiabatic or quasi-adiabatic logic families that area unit appropriate to be used in Asynchrobatic Logic. EACRL, though a lot of advanced, is additionally a comparatively straightforward by-product of those, and will be a possible candidate to be used in Asynchrobatic Logic. The multi-phase charge recovery circuits embrace clock skew, difficult power clock tree that increasing power dissipation, thus getting to use IECRL as a functional block of APL.

#### **2.3. Handshake Controllers and Fine-Grain Power-Gating**

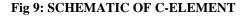

The handshaking protocols in asynchronous logic sometimes use two signals, a "request" from the sender to the receiver, and an "acknowledge" from the receiver to the sender.

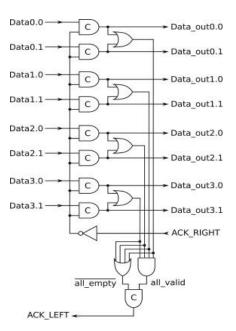

In the APL pipeline, the Handshake controller HCi in stage Si performs the subsequent tasks: 1) Detecting the validity of the inputs to the ECRL logic gates in stage Si; 2) giving power to the ECRL logic gates in stage Si; 3) detecting whether or not the outputs of stage Si are received by the downstream stage Si+2; and 4) Informing the upstream stage Si-2 once Si-2 will take away its outputs.

As illustrated in Fig. 1(a), a acknowledgment controller is comprised of a

- (i) Completion detector (CD),

- (ii) A C-element and an electrical converter.

#### **Fig 6: COMPLETION DETECTOR**

A novel completion detection system (CDS) for self-timed circuits supported current sensing has been incontestable. The CD in HCi is employed to sight whether or not the input to stage Si represents a sound codeword or an empty codeword. The output of the CD transits from LOW to HIGH once the input to stage Si becomes a sound codeword, and transits from HIGH to LOW once the input to stage Si becomes an empty codeword. If the input consists of n-bit knowledge, n pairs of wires square measure needed to encrypt the input, and also the associated CD are often enforced with a n-input C\*-element gate and n twoinput OR gates. There are two differing types of asynchronous signal conventions, two-phase and four-phase. Two-phase signal merely reacts to a modification of the signals, while four-phase signal relies upon the amount of the signals. There also are 2 totally different strategies for knowledge transmission; bundled-data and dual-rail. For various reasons, the adiabatic data-path is already dual-rail, however the chosen implementation operates victimization principles much more cherish those of bundled-data.

Fig 7: SCHEMATIC OF COMPLETION DETECTOR

The asynchronous communication happens between the Asynchronous Stepwise Charging controllers, and also the bundled-data is prevailed the adiabatic data-path. In dual-rail asynchronous logic, an identical signal protocol thereto delineated for adiabatic logic is employed. These states are accustomed perform completion detection so for a dual-rail data-path, consecutive stage are activated only if all dual-rail outputs have a sound state.

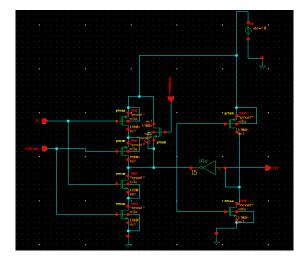

### 3. PCR mechanism and Enhanced C\*-Element

Asynchronous Logic depends upon the Muller C-Element as a principle storage element. For brevity, it'll be stated even as a "C\*-Element". The C\*-Element is as necessary to asynchronous style because the D-type Flip-Flop is to ancient synchronous style. A generalized n-input C\*-Element extends this by requiring all input to be identical before ever-changing its output state. C\*-Elements with a larger range of inputs are often enforced either directly in logic for C\*-Elements with up to four inputs, or by cascading many stages of C\*-Elements. It is conjointly attainable to feature "Reset" (to low or logic zero) or "Preset" (to high or logic one) inputs to the C\*-Element.

А

Ζ

В

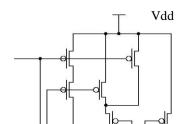

#### Fig8: STATIC C\*-ELEMENT

Figure 8 shows a circuit for a static C\*-Element. It is drawn in such some way that it around represents a stick diagrams. This suggests that the circuit's topology would be appropriate for taking the circuit to layout nearly as is. The 2 inputs square measure tagged "A" and "B" and also the output is tagged "Z". All of them use positive logic assertion levels. The standard circuit image for a C\*-Element is AND gate with a capital "C" at its centre.

The idea underlying the creation of Asynchrobatic Logic is to search out viable thanks to operate a low-power adiabatic (or quasiadiabatic) data-path asynchronously. this idea is clearly difficult as, till this point, all adiabatic logic families were documented as exploitation multiple, multi-phase power-clocks, which, in general, perform their charge exercise exploitation inductive components, whereas asynchronous logic is needed to control exploitation shake signals and to not have signals that might be outlined as a world clock. The theoretical edges of Asynchrobatic Logic from an occasional power point-of-view ought to embrace less shift losses, that are owing to

shift solely occurring once active, charge recovery and exercise, and virtually complete outpouring reduction in inactive electronic equipment, owing to the absence of any electric potential across inactive data-path components.

#### Fig 10: SCHEMATIC OF C\*- ELEMENT

Asynchrobatic Logic immensely expands the offered complexness of electronic equipment, removes clock-phase restrictions from the management logic, and as are going to be shown, permits advanced data-processing structures to be enforced in a very reusable fashion.

The control structures have to be compelled to method shake inputs from the stages adjacent to this one. Asking shake from a previous stage can indicate one amongst 2 states. Once it makes a rising zero-to-one transition, it shows that information is offered, permitting the asynchronous controller to initiate the stepwise charging method to latch that information. Conversely, once it makes a falling one-to-zero transition, it indicates that the charge on the inputs has been recovered, which the asynchronous controller ought to initiate the stepwise discharging method to recover the charge. relying upon the direction of its transition, associate acknowledge from the next stage can either indicate that it's within the "Idle" state which its inputs is also modified, or that it's evaluated its inputs which charge recovery could start. For straightforward pipeline stages, these acknowledgments are often achieved exploitation solely a C\*-Element, as represented. Then would be Asynchrobatic logic additional economical. It ought to be noted that IECRL may be a quasi-adiabatic logic family, therefore by exploitation absolutely adiabatic, reversible logic structures, it's doubtless that the data-path's power consumption are often additional down.

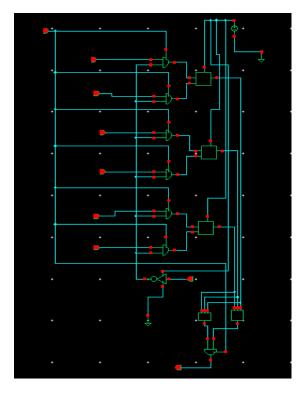

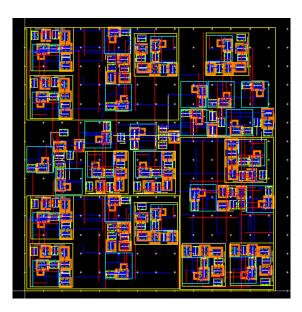

#### Fig 11: LAYOUT OF APL

However, not like the bulk of ancient CMOS-based logic systems, Asynchrobatic Logic doesn't perform sign employing a single wire to represent one bit. Slightly is described on 2 wires, with 3 outlined states, one invalid state and also the risk of assorted indefinite states at format.

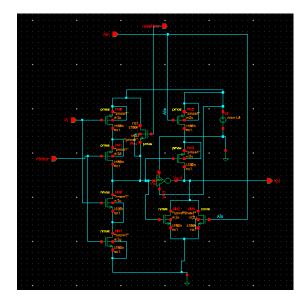

#### 4. Simulating results

#### 4.1. Circuit level simulation

Since Cadence tools exist to simulate circuits, but the employment of SPICE presents few major issues. There is a minor issue that requires being thought-about. There are alternative accuracy problems with Cadence including the parameters and numerical simulation technique. Alternative problems relate to making sure that the item of simulation details are measure correct, and to properly measurement the simulated power dissipation.

The VT of devices failed to have to be compelled to be thought-about for either the zero.8µm or 0.35µm processes as just one was offered. The device filler employed in the adiabatic data-path was minimum length and minimum dimension. The connections to the majority terminals were created as follows. All NMOS devices had their bulk terminal connected to ground. The cross-coupled PMOS devices within the data-path had their bulk terminal connected to the power-clock. this permits them to recover additional charge through their internal diode, except for full-layout simulations, it might be necessary to model the reverse-biased n-well to psubstrate diode that may be created.

For circuits that have a physical layout implementation, a full parasitic extraction of a minimum of resistance and capacitance ought to be performed, and this was finished the initial presentation of Asynchrobatic Logic. the following works used front-end SPICE internet lists that square measure internet lists containing solely ideal devices while not these parasitic, that means that the quoted performance figures square measure doubtless to be optimistic.

A serious use of Cadence was to measure power consumption, as this can be performed. The initial measurements of power consumption were performed by victimization additional pseudocircuits to perform these measurements. These pseudo-circuits consisted of a current-controlled voltage supply, controlled by the voltage supply underneath observation, driving a capacitance. This performed the mixing of this with relevancy time to permit the ability to be calculated.

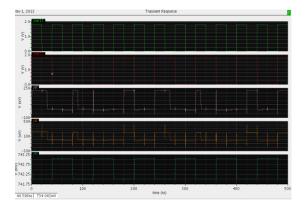

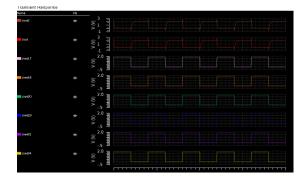

Fig 12: SIMULATION WAVEFORM FOR APL-PCR

The power comparisons of AFPL circuit with ECRL and APL circuit with I-ECRL are unit performed. In existing methodology compared with static CMOS counterpart, the AFPL w/o PCR will scale back static power dissipation by 83.1%, and therefore the AFPL-PCR implementation will scale back static power dissipation by 85.5%. In projected methodology, compared with static CMOS APL w/o PCR will scale back power dissipation by 83.3%, and therefore the APL-PCR will scale back power dissipation by 87.8%. Finally, eight bit K-S adder is intended with APL pipeline circuit and their power is calculated mistreatment Xilinx implementation.

Fig13: TRANSIENT RESPONSE FOR APL-PCR

#### 5. Conclusion

Leakage power contributes to the next proportion in total power dissipation in VLSI circuits. This leak power reduces circuit dependability as whole. During this paper, a completely unique technique to cut back leak power has been projected. In projected methodology, compared with static CMOS AFPL-PCR will scale back power dissipation by 83.3%, and therefore the APL-PCR will scale back power dissipation by 87.8%. Logical effort ideas will extend this paper & get additional optimum results.

#### References

[1] Yong Moon and Deog-Kyoon Jeong, "Efficient Charge Recovery logic," 1995 Symposium on VLSI Circuits - Digest Technical Papers, pp. 129-130, Kyoto, Japan, 8<sup>th</sup>-10<sup>th</sup> June 1995.

[2] Yong Moon and Deog-Kyoon Jeong, "An Efficient Charge Recovery logic circuit," IEEE Journal of Solid-State Circuits, 31(4): 522, April 1996.

[3] J. S. Denker, "A review of adiabatic computing", 1994 IEEE Symposium on Low Power Electronics – Digest of Technical Papers (ISLPE'94), pages 94-97, San Diego, California, USA, 10<sup>th</sup>- 12<sup>th</sup> October 1994.

[4] L. Heller, W. Griffin, J. Davis and N. Thoma, "Cascode voltage switch logic: a differential CMOS logic family", IEEE International Solid State Circuits Conference – Digest of Technical Papers (ISSCC'84), pages 16–17, San Francisco, California, USA, February 1984.

[5] A. Kramer, J.S. Denker, B. Flower and J. Moroney, "2<sup>nd</sup> Order adiabatic computation with 2n-2n2p logic circuits", IEEE Journal of Solid-State Circuits, lifomia, USA, February 1984.

[6] F.Liu and K.T. Lau, "Improved structure for efficient charge recovery logic," Electronics Letters, 34(18): 1731-1732, 3<sup>rd</sup> September 1998.

[7] Jens sparso and Steve furber (editors.), "Priciples of Asynchronous Circuit Design: A Systems Prespective", Kluwer Academic Publishers, Dordrecht, The Netherlands, 2001. ISBN: 0-7923-7613-7. ISBN13: 9780792-376132

[8] K.van Burgess, J. Kessels, M. Roncken, F. Schalij and A. Peeters, "Asynchronous circuits for low power: a DCC error corrector", IEEE Design and Test of computers. 11(2):22-32, Summer 1994.

[9] A. Vetuli, S. D. Pascoli and L.M. Reyneri. "Positive feedback in adiabetic logic", Electronic Letters, 32(20): 1867-1869, 26<sup>th</sup> September 1996.

[10] David J.Willingham and Izzet Kale, "Using Positive Feedback Adiabetic Logic to implement Reversible Toffoli Gates", Proceedings of Norchip 2008, paes 5-8, Tallinn, Estonia, 17<sup>th</sup> -18<sup>th</sup> November 2008.

[11] David J.Willingham and Izzet Kale, "Asynchronous, quasi- Adiabetic (Asynchrobatic) logic for power very wide data width applications", Proceedings of International Symposium n Circuits and Systems (ISCAS 2004), volume 2, pages II: 257-260.

[12] David J.Willingham, "Variations in Power Consumptions of Adiabetic Logic Families depending upon the Charging Scheme used", 2005, unpublished.

[13] Nigel C. Paver, "The Design and Implementation of an Asynchronous Microprocessor", Ph.D. Thesis, University of Manchester, UK, 1994.

[14]Handshake Solutions, URL: http://www.handshakesolutions.com/.

[15] A. Blotti. S. Di Pascoli and R. Saletti," A comparision of some circuit schemes for semireversible adiabetic logic", International Journal of Electronics, 89(2): 147-158, February 2002.

[16] M.C. Chang Wei-Hsiang Chang, 'Asynchronous Fine-Grain Power-Gated Logic," in Proc. Int. Midwest Symp. Circuits Syst., 2009, Pg.1143-1153.

[17] Asynchrobatic Logic for Low-power VLSI Design David John Willingham, March 2009.

[18] Yong Moon and Dong- Kyoon jeong, "An efficient charge recovery logic circuit", IEEE Journal of Solid-State Circuits, 31(4):514-522, April 1996.

[19] M.Arsalan and M. Shams,"Asynchronous adiabetic logic", inn Proc. IEEE Int. Symp. Circuits Syst., May 2007, pp. 3720-3723.